CPU의 구성

- 제어장치: 명령어를 해석하고 실행(각 장치들을 제어)

- 연산장치(ALU, Arithmetic and Logic Unit, 산술 논리 연산장치): 연산 기능 수행

- 레지스터 파일: 데이터를 보관

- CPU 버스: 구성 요소들을 연결

연산 장치가 제공하는 연산의 종류

- 산술 연산: 덧셈, 뺄셈 등

- 논리 연산: AND, OR 등

- 기타 연산: 시프터(비트 shift), 보수기(비트 반전) 등

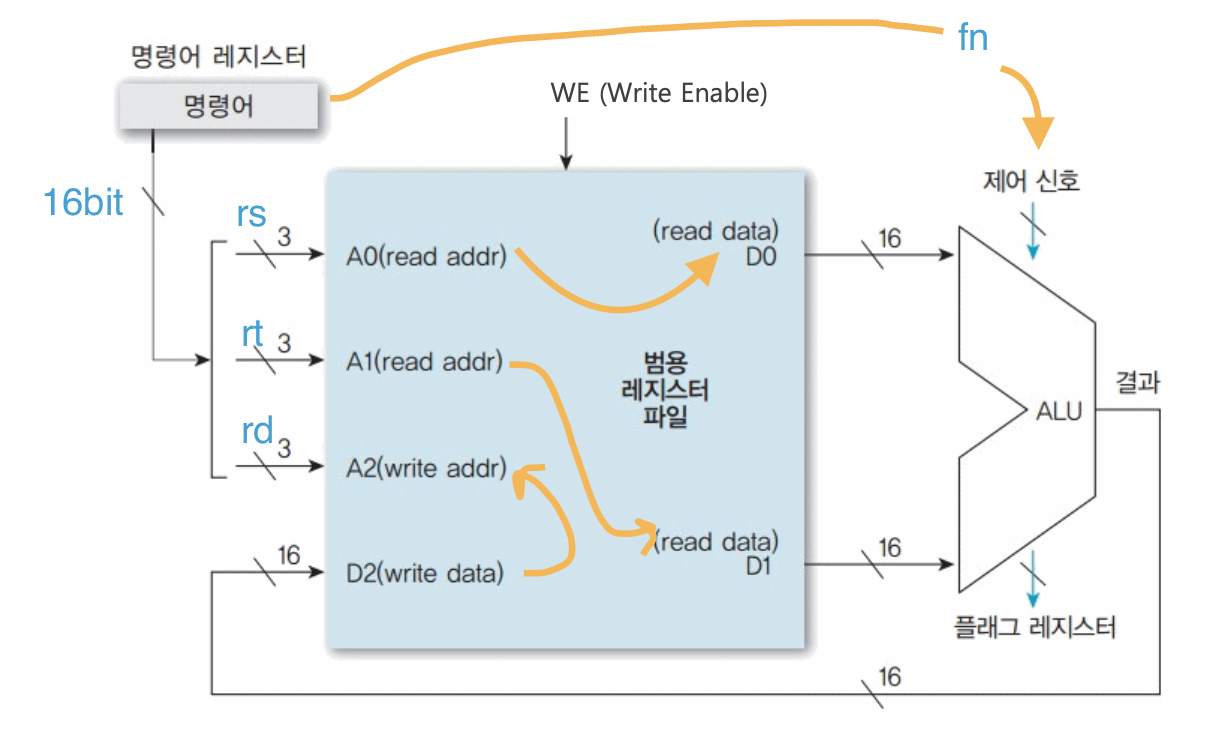

picoMIPS R-형식 명령어 처리 과정

- 연산장치와 레지스터 파일

- 레지스터 파일은 연산장치가 처리하는 데이터의 근원지이자 목적지

예제

- 범용레지스터파일: 레지스터 묶음, 레지스터 주소로 구분됨, 레지스터는 워드 단위로 저장, 여기서는 16bit

- 3번 레지스터 값 + 4번 레지스터 값 ⇒ 5번 레지스터에 저장

- 010 = add 명령

- 레지스터 파일 안의 값들은 현재 레지스터가 저장하고 있는 값

- 위에서부터 레지스터 0~7

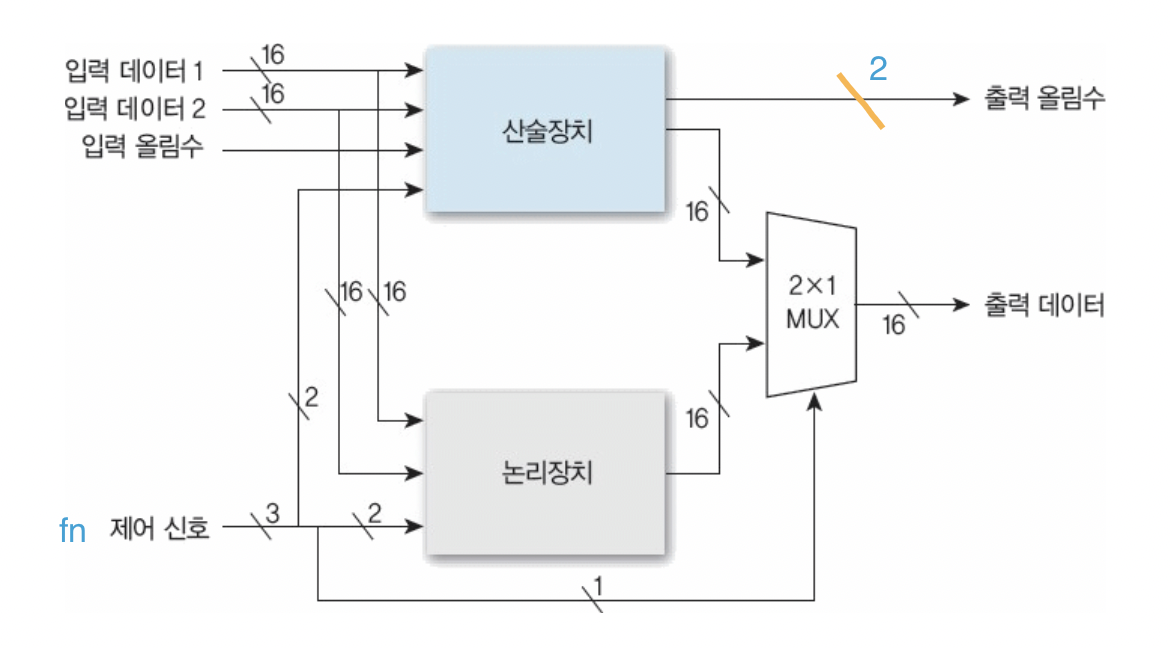

산술장치와 논리장치의 통합

- MUX(multiplexer, 멀티플렉서)를 이용한 16비트용 연산장치

- alu 내부에 산술, 연산 장치 구분되어 o

- 입력 올림수 = 캐리

- mux: 두 세트의 신호에서 제어신호에 따라 산술장치 Or 논리장치의 값을 선택할지 선택해 데이터 출력

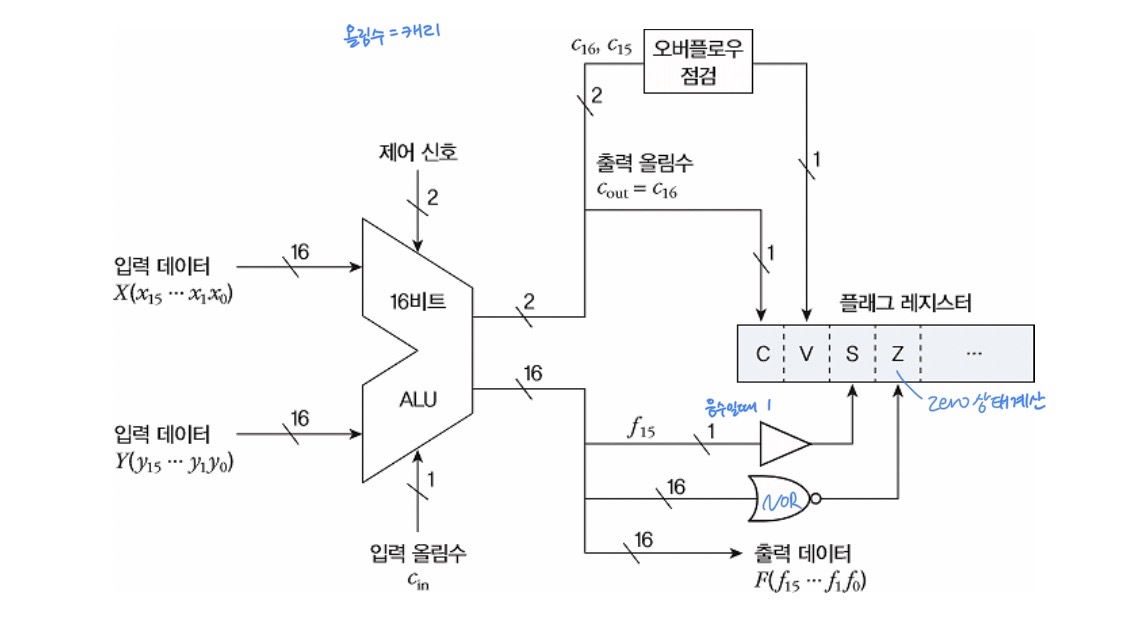

플래그 레지스터

- CPU의 연산과정 중에 발생한 상태를 보관하기 위한 레지스터

- C: Carry, V: Overflow, S: Sign, Z: Zero 등

- 연산값이 나오는 것과 별개로 캐리, 오버플로, 사인 부호, 제로인지 상태 보관하는 레지스터

Uploaded by N2T

'이론 > 컴퓨터구조' 카테고리의 다른 글

| 데이터 경로 (1) | 2024.01.09 |

|---|---|

| 정수, 부동소수점 연산 (1) | 2024.01.06 |

| 실수, 비수치 데이터 (1) | 2023.12.24 |

| 데이터 형식, 정수 (1) | 2023.12.06 |

| 복잡도에 따른 명령어 집합 (1) | 2023.12.04 |

댓글